選擇會議平板為什么推薦選電容的?有什么門道嗎?

2020-03-02 08:00:37

中視智能商顯科技

386

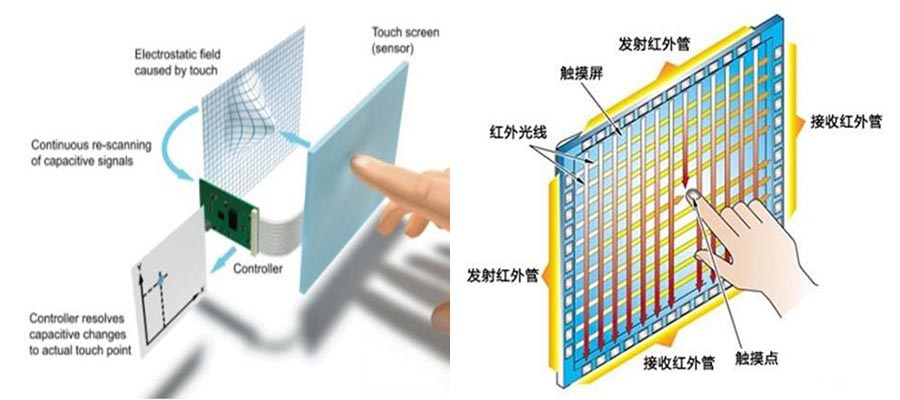

為什么說選擇會議平板的時候要選擇電容屏的?有什么講究呢?電容屏會議平板有哪些好處?為什么要舍棄紅外屏會議平板一體機?今天跟隨中視智能一起來看看這其中的原因,首先,我們要先了解電容觸控跟紅外觸控的區別,如下圖:

1、始于顏值,終于才華

找遍市面上的會議平板產品,我們不難發現,所有的紅外觸控屏會議平板都會有一圈凸起的邊框,而電容式觸控屏的邊框跟我們的屏幕在同一個平面上,沒有凸起,純平跟凹凸之間,顏值瞬間就體現出來了,我們可以想象一下,如果我們手機的邊框加上厚厚的一層,集塵就不說了,那外觀......

2、電容觸控屏會議平板不會存在誤觸現象

因為非透明物體都能夠擋住紅外涉嫌,所以,除了透明的物體,其他的基本上所有東西都能夠在紅外屏會議平板上實現觸控,比方說我們冬天的羽絨服,在冬季開會,穿著厚厚的衣服操作會議平板的時候,衣服非常容易碰到屏幕;然而電容式會議平板因為只能感應到手指以及電容筆的觸摸行為,所以能夠放心的書寫跟批注,杜絕了誤觸的可能性;

3、對使用環境的要求

紅外發射器的感應機制容易受到強光、水潑以及蚊蟲的印象概念股,素偶偶,紅外式會議平板在一些特定的情況下無法使用,戶外有強光照射的地方、水滴濺到屏幕上以及蚊蟲比較多的場景,紅外觸控屏會議平板的使用效果都會大打折扣,但是電容式會議平板在這樣的場景中完全不會受到干擾,能夠正常的進行工作;

通過以上的三點分析,所以,您現在知道為什么要選擇電容式會議平板了吧,深圳中視智專注于中高端會議平板以及教學一體機的研發與生產制造,如果您有相關的產品需求,歡迎您致電中視,我們將為您提供完善的產品解決方案與優質的服務。